-

Notifications

You must be signed in to change notification settings - Fork 108

Home

OpenFPGA development made easy

- FPGA development board (iCE40HX1K-TQ144 from lattice)

- Open hardware

- Compatible with the opensource icestorm toolchain

- Multiplatform: Linux / Mac / Windows

- Arduino like board: similar pinout than Arduino one / BQ zum.

- You can Reuse most of available Arduino / Zum shields

- Control your robots / printbots from an FPGA

- 12 MHZ MEMS oscillator

- ON/OFF switch (turn off your mobile robot easily)

- Input power voltage: 6 - 17v

- Max input current: 3A (Perfect for powering your robots)

- 20 Input/output 5v pins

- 8 Input/Output 3.3V pins

- USB micro-B connector for programming the FPGA from the PC (same than zum board)

- FTDI 2232H USB device allows FPGA programming and UART interface to a PC

- Reset pushbutton

- 8 general purpose leds (user leds)

- 2 general purpose pushbuttons

- 4 analogue inputs though I2C bus

This board is about exploring the opensource side of the FPGAs. We know that there are more powerful FPGAs. We know that the are very very very amazing software tools that can do a lot of stuff... but they are not opensource. So, if you like the freedom too, this board is for you

| Image | Description |

|---|---|

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/2016-03-04-Mounting-first-prototype/icezum-alhambra-1.jpg | width=400px]] |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/2016-03-04-Mounting-first-prototype/icezum-alhambra-2.jpg | width=400px]] |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/2016-03-04-Mounting-first-prototype/Icezum-alhambra-test-1.jpg | width=400px]] |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/2016-03-04-Mounting-first-prototype/Icezum-alhambra-test-3.jpg | width=400px]] |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/2016-03-04-Mounting-first-prototype/Icezum-alhambra-test-5.jpg | width=400px]] |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/Icezum-rev1-1607-img1-peq.png | width=400px]] |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/Icezum-rev1-1607-img2-peq.png | width=400px]] |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/Icezum-rev1-1607-img3.png | width=400px]] |

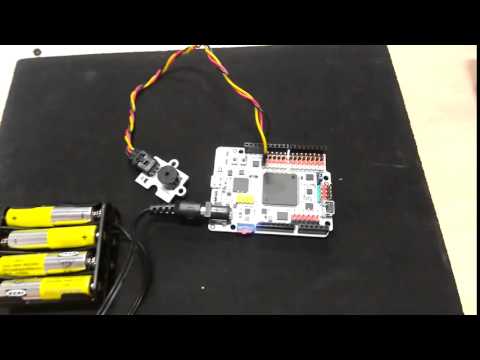

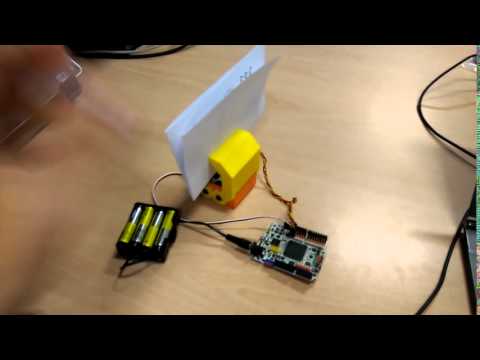

Examples of use of the IceZUM Alhambra board. All of them are hardware: there is no cpu, no software, no libraries, just plain hardware on the FPGA :-)

| Image | Description |

|---|---|

|

Playing the imperial march :-) (VIDEO) |

|

Opening and closing a 3D printer gripper with a pushbutton (VIDEO) |

|

Testing an IR sensor (VIDEO) |

|

A 3D-printed robot following a black path (VIDEO) |

|

Locomotion of a 3D-printed caterpillar-like robot (VIDEO) |

|

Verilog-to-Bitstream Flow for iCE40 FPGAs in an ubuntu phone (VIDEO) |

All the design files are locate in the github repo: schematics, PCB, BOM and GERBER files for manufacturing. This initial version (Rev 1.0) has been designed with Altium, but it is being migrated to Kicad.

Update May/30/2016: The schematics have been fully migrated to kicad (folder)

All the 3D models have been designed using the opensource tool Freecad. In this table you can see the 3D components, the step files and their sources in Freecad. All the sources are located in the Freecad Parts library

| 3D component | Footprint | Step | Freecad | Description |

|---|---|---|---|---|

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/C_0402-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/C_0402-footprint.png | width=200px]] | C_0402.step |

| [[https://github.com/FPGAwars/icezum/raw/69fdcb15a7aceb848f183d0d624d8274737c5b4b/wiki/V1.0K/3D-components/C_0603-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/C_0603-footprint.png | width=200px]] | C_0603.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/C_1206-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/C_1206-footprint.png | width=200px]] | C_1206.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SOD-323-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SOD-323-footprint.png | width=200px]] | SOD-323.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/LED_0603-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/LED_0603-footprint.png | width=200px]] | LED_0603.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/DO-214AC-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/DO-214AC-footprint.png | width=200px]] | DO-214AC.step.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SOT-23-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SOT-23-footprint.png | width=200px]] | SOT23-3.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/F_1812-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/F_1812-footprint.png | width=200px]] | F1812-505k.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SOT-563-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SOT-563-footprint.png | width=200px]] | SOT-563.step.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/USB_micro-B-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/USB_micro-B-footprint.png | width=200px]] | USB-micro-B.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x6-pin-header-2.54mm-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x6-pin-header-2.54mm-footprint.png | width=200px]] | 1x6-pin-header.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x6-socket-header-2.54-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x6-socket-header-2.54-footprint.png | width=200px]] | 1x6-socket-h.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x10-socket-header-2.54-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x10-socket-header-2.54-footprint.png | width=200px]] | 1x10-socket-h.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x8-socket-header-2.54-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x8-socket-header-2.54-footprint.png | width=200px]] | 1x8-socket-h.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x8-pin-header-2.54mm-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x8-pin-header-2.54mm-footprint.png | width=200px]] | 1x8-pin-header.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x4-pin-header-2.54mm-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x6-pin-header-2.54mm-footprint.png | width=200px]] | 1x4-pin-header.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/jack_2.1-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/jack_2.1-footprint.png | width=200px]] | jack-2.1mm.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/2x4-pin-header-2.54mm-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/2x4-pin-header-2.54mm-footprint.png | width=200px]] | 2x4-pin-header.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x3-pin-header-2.54mm-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/1x3-pin-header-2.54mm-footprint.png | width=200px]] | 1x3-pin-header.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/L_0805-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/L_0805-footprint.png | width=200px]] | L_0805.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/L_0603-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/L_0603-footprint.png | width=200px]] | L_0603.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/L_4040-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/L_4040-footprint.png | width=200px]] | L_4040.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/DFN-2523-6-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/DFN-2523-6-footprint.png | width=200px]] | DFN2523-6.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/R_0402-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/R_0402-footprint.png | width=200px]] | R_0402.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/R_Array_4x0603-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/R_0402-footprint.png | width=200px]] | R_Array_4x0603.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SW_smd_60x3.8-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SW_smd_60x3.8-footprint.png | width=200px]] | sw_smd_6.0x3.8.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/slide-sw-spdt-right-angle-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/slide-sw-spdt-right-angle-footprint.png | width=200px]] | slide-sw-spdt.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SW_vert_tht_7.5x6x6.5-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/SW_vert_tht_7.5x6x6.5-footprint.png | width=200px]] | sw-vert-tht.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/TQFP-144_IPC-MD-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/TQFP-144_IPC-MD-footprint.png | width=200px]] | TQFP-144-iCE40.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/DFN-8-6X5mm-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/DFN-8-6X5mm-footprint.png | width=200px]] | DFN-8-6x5mm.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/FTDI-QFN-64-footprint-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/FTDI-QFN-64-footprint.png | width=200px]] | FTDI_QFN-64.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/Xtal-3_2x2_5-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/Xtal-3_2x2_5-footprint.png | width=200px]] | Xtal-3_2x2_5.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/MSOP-8_3x3mm_Pitch0.65mm-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/MSOP-8_3x3mm_Pitch0.65mm-footprint.png | width=200px]] | MSOP-8_3x3mm.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/VQFN16-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/VQFN16-3D.png | width=200px]] | PVQFN16.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/QFN16-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/QFN16-footprint.png | width=200px]] | QFN16.step |

| [[ | width=200px]] | [[ | width=200px]] | .step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/DFN-3030-8-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/DFN-3030-8-footprint.png | width=200px]] | DFN_3030-8.step |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/WSON-6-3D.png | width=200px]] | [[https://github.com/FPGAwars/icezum/raw/master/wiki/V1.0K/3D-components/WSON-6-footprint.png | width=200px]] | WSON-6.step |

-

I am new to FPGAs. Is this board ok for me?

Absolutely. This board is intended for people that never has designed a digital circuit and want to learn the basics. Learn how to create simple combinational circuits for controlling robots. Learn how the counters, pwm units, uarts and other devices works, using easy to plug sensors and actuators. Learn to think in a "hardware way" instead of software way. Synthesize your own small processors. This board is about learning digital electronics easily, using only opensource tools. -

Why are you using Lattice ICE40 FPGA instead of the very well known ones from Xilinx or Altera?

Because the ICE40 family from Lattice is (currently) the only one that has a fully opensource toolchain. Have a look at the Icestorm project by Clifford Wolf. We really believe that this project is going to change everything. This is like the gcc toolchain for the hardware world -

Why are you using the horrible arduino pinout?

Just for reusing some already made shields. This board is about learning, not creating a new "standard". There are hundreds of already working arduino shields. Why not reusing them? Designing hardware for using these shields would be fun. In addition, the IceZUM Alhambra has three-pin connectors to attach directly servos or sensors easily, without having to plug shields. -

Where are the rest of the FPGA I/O pins?

They are gone. For teaching digital electronics and learning with small projects we think that 20 I/O pins are more than enough -

I know nothing about HDL languages. Is there any software I can use for uploading hardware into the board?

Yes. We are working on the Icestudio tool. It is an opensource multiplatform tool (releases under the GPL license). Currently is very limited but we are improving it so that people can learn the basis of digital design. And the community can modify it. -

I want to develop some cores, but using HDL languages. Is it possible? Of course. You can directly write your programs in Verilog and use the Icestorm toolchain for synthesizing and uploading the hardware. If you are not a beginner, you can choose the tools you want

-

I know VHDL language and do not want to use Verilog

Currently, the Icestorm toolchain only supports verilog. But as these is an opensource project, we are sure that the community will support it in the future -

But for learning and making simple circuits is better to use an CPLD. Why using an FPGA?

Because we do not know of any CPLD with an fully opensource toolchain. For educational purposes, we think that the software should be opensource -

Why should I prefer the IceZUM board instead of Papilio, that is much more powerful? Because the Papilio boards are based on Xilinx FPGAs, that do NOT have opensource tools for generating the bitstreams. You need the propietary tools from Xilinx. IceZUM board is about freedom

-

2016/05/30: Icezum schematic migrated to Kicad! (Folder)

(Large image) -

2016/05/18: Icezum pinout migrated to SVG, so that anyone can open / edit / modify it using inkscape (only opensource tools) (Repo folder)

(Large image) -

2016/05/04: Alberto Piganti has made a wonderful pinout ¡Thanks!

(Large image) -

2016/03/08: The first 5 prototypes are ready! :-)

(Large image) -

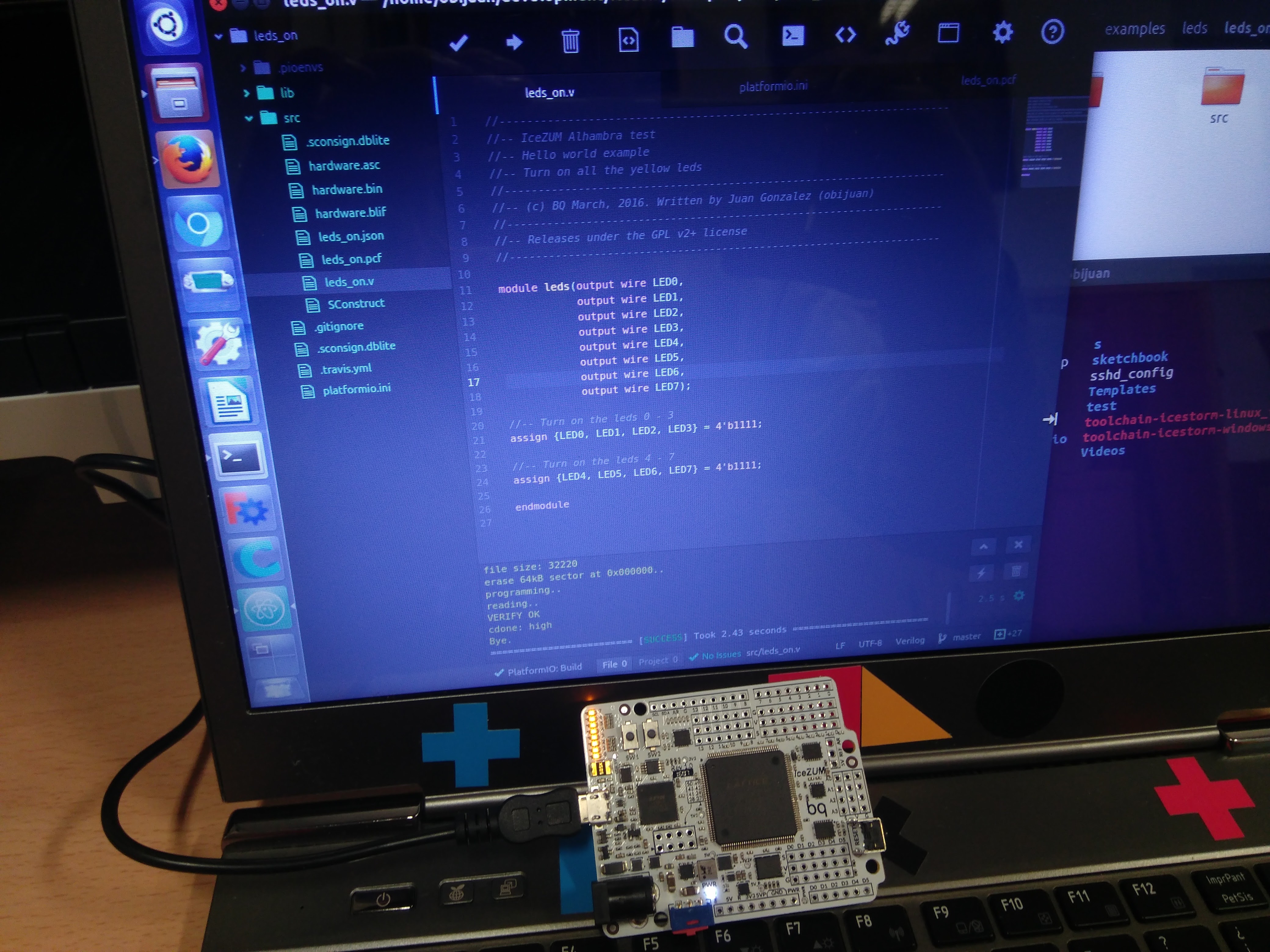

2016/03/07: First bitstream downloaded into the IceZUM Alhambra from GNU/Linux Ubuntu 15.10. Using platformio-fpga and the Icestorm toolchain

-

2016/03/05: First bitstream downloaded into the IceZUM Alhambra! The test has been done with the iceprog cross-compiled for windows

-

2016/03/04: Soldering and initial tests

-

2016/03/03: ¡The first PCBs have arrived! :-) (Image)

-

2016/02/28: This flavour of icezum will be called Icezum Alhambra. The name was suggested by Sebastián Gallardo in this post in the FPGA-war spanish google group. The Author (Eladio Delagado) is from a small town in Granada, called Pinos del Valle

-

2016/02/27: The PCBs have been already manufactured by pcbway and they are sending them. The estimated delivery date is March 03 2016. Can't wait to have then in our hands!

-

2016/02/22: Components from Farnell has arrived!

-

2016/02/19: Initial components for mounting the prototypes has arrived! :-)

| Image | Description |

|---|---|

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/icezum-rev1-1607-components-1.jpg | width=200px]] |

| [[https://github.com/FPGAwars/icezum/raw/master/wiki/icezum-rev1-1607-components-2.jpg | width=200px]] |

- 2016/02/18: PCB Initial version (rev 1.0-1607) is sent for manufactoring. 5 units for testing. Manufacturer: pcbway

- V1.0: Eladio Delgado Mingorance, from Pinos del Valle, Granada, Spain. Sponsored by BQ

- V1.0K: Migrated to Kicad by Juan González (Obijuan). 3D models designed with FreeCAD. Everything is generated using only opensource tools (schematics, pcb, 3D models, pinout, BOM...). This version belongs to our Technological Heritage

- BQ. Thanks for funding this project from 2015-12-20 to 2016-04-14. During this period, the icezum V1.0 was born and 10 prototypes were manufactured.

- María Delgado Mingorance, for helping in the manufacturing and design of the V1.0

- V1.0 was derived from the Arduino Uno board

- V1.0 was derived from the zum core board by BQ

- V1.0 was derived from the Icestick by Lattice

- Icestorm project, by Clifford Wolf and Mathias Lasser

- Icezum Pinout, by Alberto Piganti

- Jairo Zerberos. Migration of the FT2232H schematic symbol from altium to kicad. Thanks!

- altium2kicad. Tool used for the migration from Altium to Kicad. Many thanks to the developers!

- Kicadstepup. Tool for exporting the board to FreeCAD

- Juan González (Obijuan): V1.0 specifications. Migration to Kicad (V1.0K)

- Alhambra festival picture, by Cristina Urdiales. Thanks for this beautiful paiting!

- Many thanks to BQ, for funding the initial prototype V1.0, during the period 2015-12-20 to 2016-04-14. Thanks a lot for increasing our technological heritage by sponsoring openhardware boards.

Licensed under Creative Commons Attribution-ShareAlike 4.0 International License